A Guide to Key PIC Industry Design Guidelines for Optimizing Performance and Scalability

A Short Guide to Key PIC Industry Design Guidelines for Optimizing Performance and Scalability

Introduction

Photonic integrated circuits (PICs) are advanced semiconductor devices that integrate various photonic components, including lasers, detectors, and modulators, onto a single chip, enabling efficient manipulation and transmission of optical signals for faster data transmission, enhanced signal quality, and lower power consumption.

The PIC industry has seen a surge in applications across various sectors, including telecommunications, data centers, biomedical devices, and quantum computing, driven by the demand for high-speed data transmission and enhanced functionality in compact form factors.

According to a recent market report, the silicon PIC market was valued at $95 million in 2023 and is projected to exceed $863 million by 2029, with a booming compound annual growth rate (CAGR) of 45%. To capitalize on this opportunity, it is crucial to understand the key design principles and guidelines that govern the PIC industry.1

This article serves as a helpful guide, highlighting key PIC industry design guidelines essential for optimizing performance and scalability.

Global Photonics Engineering ContestThis engineering challenge invites engineers, innovators, and startups to push the boundaries of Photonic Integrated Circuits (PIC) and create applications that address complex engineering challenges and push the boundaries of the industry. Whether you’re in semiconductors, data & telecom, medtech, or agritech, we want to see your breakthrough idea that can harness the power of PICs to change the world.

|

Industry Design Guidelines for PICs

Standard Design Methodologies

Designing for Scalability

Transitioning from prototype to mass production of PICs presents significant challenges that demand adherence to design guidelines for consistent performance and scalability. For instance, minimizing optical losses is critical and is achieved through optimized waveguide geometries and advanced fabrication techniques to reduce scattering losses.

Reducing component footprints is also crucial for scalability, as compact designs enable higher integration densities and lower production costs. Strategies using tight bends from high-index contrast waveguides and innovative geometries like spiral delays help achieve this goal while balancing performance and manufacturing constraints.

Moreover, implementing redundancy and error tolerance mechanisms enhances manufacturing yield. This can involve incorporating backup components that activate upon failure of primary ones and employing design strategies, such as using adiabatic couplers instead of directional couplers, to increase resilience to fabrication variations.2

Low-Loss and High-Speed Design

The demand for high-speed data communication has accelerated advancements in PICsparticularly in optical waveguides . Therefore, optimizing waveguide design is essential to enhance performance metrics such as insertion loss and crosstalk.

Minimizing Bending Losses: Bending regions in waveguides can cause losses due to mode mismatching, radiation, and scattering. To mitigate these issues, tapered waveguide bends, multimode interference structures, and adiabatic bends are used to reshape the waveguide or gradually vary the refractive index along the bend, reducing losses to below 0.01 dB for a single 90-degree bend.

Optimizing Waveguide Intersections: Waveguide intersections are crucial for signal manipulation in PICs but can increase insertion loss and crosstalk. Optimization techniques like tapered junctions and multi-step transitions enable adiabatic mode transformations, reducing insertion loss to below 0.05 dB and crosstalk to below -25 dB.

Enhancing Structural Quality: Improving sidewall roughness, varying waveguide heights, and using shallow etch techniques enhance performance.

Material selection and advanced fabrication techniques are critical for achieving optimal performance in PICs. For example, silicon nitride is favored for its exceptionally low optical loss (typically below 0.1 dB/cm), indium phosphide is essential for active components due to its direct bandgap for efficient light emission, and lithium niobate is preferred for high-speed modulators because of its excellent electro-optic properties. Similarly, techniques like deep ultraviolet (DUV) lithography and electron beam lithography enable high-resolution patterning of waveguide structures, enhancing design precision and minimizing optical losses. Chemical vapor deposition (CVD) is also instrumental in depositing uniform thin films with controlled material properties, which are essential for creating waveguides with low propagation loss and high signal integrity.

The careful selection and optimization of fabrication methods and materials substantially improve the optical performance of photonic integrated circuits, resulting in reliable and efficient photonic systems.3

Thermal Management and Power Consumption

PICs are highly sensitive to temperature variations, requiring advanced thermal management solutions to ensure reliable performance. For instance, in silicon photonics-based systems, a temperature fluctuation of just 10 ºC can cause channel-hopping in dense wavelength division multiplexing (DWDM) systems, leading to significant degradation in signal integrity and overall system performance.

Currently, two thermal management approaches are employed in PICs: passive and active cooling.

Passive cooling creates a low thermal resistance path from the PIC to the module housing, enabling external conductive or convective cooling but relying on housing temperature. Meanwhile, active cooling uses a thermo-electric cooler (TEC) between the PIC and housing, allowing independent temperature control with a thermistor and control circuit despite increasing thermal resistance.4,5

However, effective heat dissipation management in densely integrated systems requires following additional strategies to prevent overheating and ensure reliable operation.

Thermal Isolation Techniques: Utilizing thermal barriers or materials with low thermal conductivity minimizes heat transfer between densely packed components.

Circuit Layout Optimization: Enhancing airflow and thermal distribution through optimized circuit layouts and appropriate spacing between components facilitates convection and radiation of heat.

Power Consumption Reduction: Lowering power consumption through optimized operating voltage current and using low-power components reduces overall heat generation.

Chip and Package-Level Optimization: Using optimized device geometries, low-loss materials, and effective packaging solutions enhances heat dissipation.

Thermal Modeling and Monitoring: Employing thermal modeling tools for predicting temperature distribution and implementing temperature monitoring systems ensures effective management of thermal performance.6

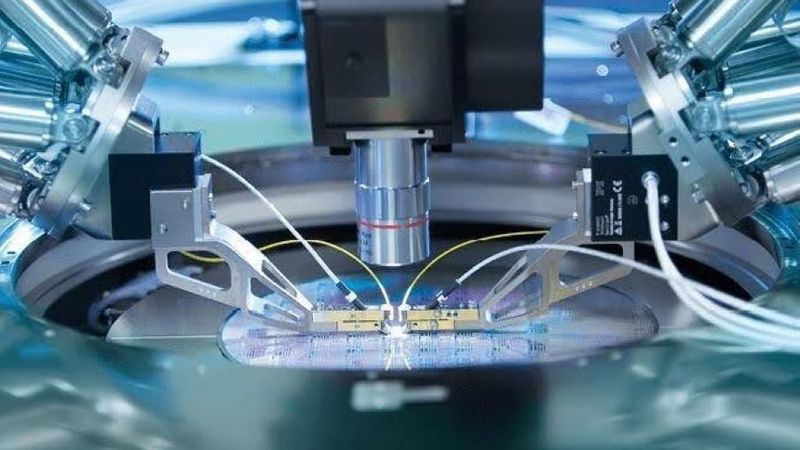

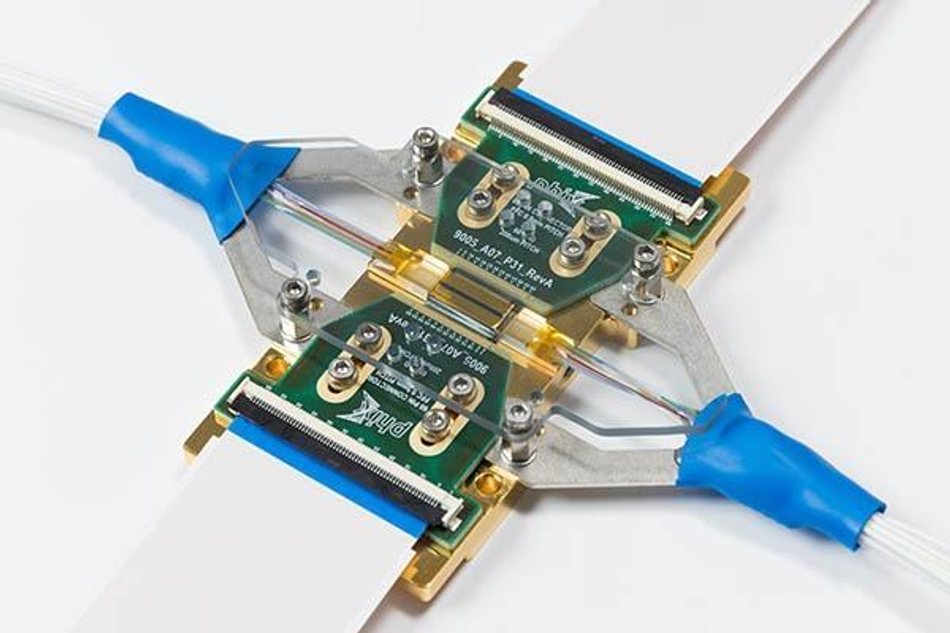

PIC from PHIX. Credit: PHIX

PIC from PHIX. Credit: PHIX

Design Automation and Simulation Tools

Modern PIC design relies on advanced software solutions for accurate modeling, simulation, and optimization. Industry leaders have developed comprehensive tools known as photonic design automation (PDA) to tackle the complexities of photonic design.

These tools enable engineers to evaluate various design scenarios—such as geometric variations, material selections, and environmental factors—thus minimizing design errors, reducing fabrication costs, and accelerating the time-to-market for new devices.7

Lumerical, a leading provider of photonic design software, specializes in advanced optical modeling solutions for analyzing complex waveguide structures. Synopsys facilitates complex circuit design with its OptoDesigner software, ensuring high manufacturability through process design kits (PDKs).

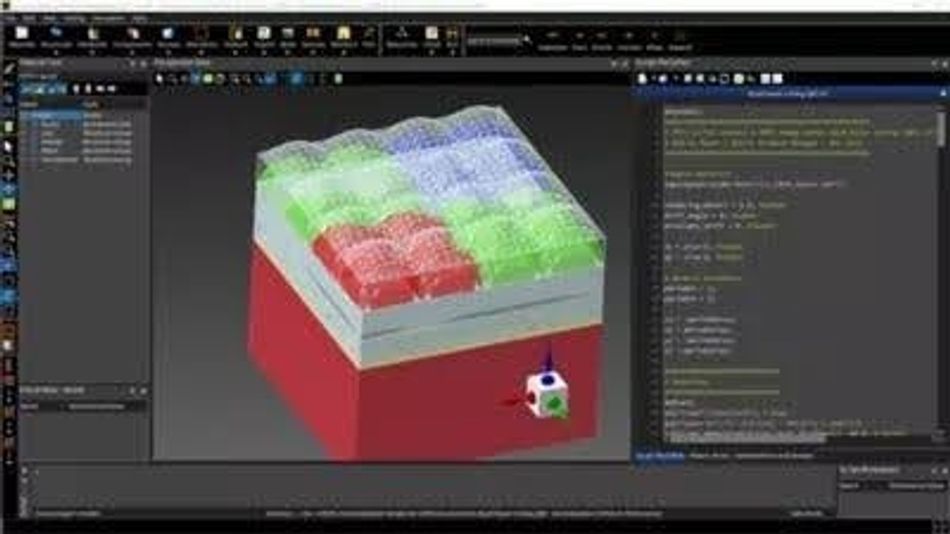

Ansys offers a comprehensive suite of simulation tools, including HFSS for detailed 3D modeling, which can predict the microwave behavior and simulate S-parameters for high speed applications.

Recently, it developed an electronic photonic design automation (EPDA) solution, enabling the co-design and co-simulation of electronic and photonic components, thereby enhancing design workflows and optimizing performance through advanced modeling techniques, including photonic Verilog-A models.8

Ansys Lumerical FDTD is used to model nanophotonic devices, processes, and materials. Credit: Ansys.

Ansys Lumerical FDTD is used to model nanophotonic devices, processes, and materials. Credit: Ansys.

Common Simulation Methodologies

The PIC industry employs various key simulation methodologies, each suited to specific design applications.

The beam propagation method (BPM) is one of the first widely adopted techniques for modeling axial light propagation in photonic devices, particularly effective for simulating weakly guiding structures such as long, gradually varying waveguides. However, BPM encounters limitations with high index contrast materials and large angle bends, necessitating alternative methods in these cases.

Finite-difference time-domain (FDTD) simulation serves as the primary technique for solving Maxwell's equations in complex photonic structures, enabling accurate modeling of intricate nanoscale geometries while providing broadband results through parallelization; however, its computational intensity can challenge simulations of large structures.

The Eigenmode expansion method (EME) complements these approaches by efficiently managing multiple modes and polarizations for long-distance propagation analysis, making it ideal for studying waveguide coupling and mode evolution.9

Design Rule Checking (DRC)

Verification is crucial in the PIC design process, ensuring that designs comply with foundry requirements and are manufacturable.

Commercially available industry-standard tools such as Cadence Physical Verification System, and Synopsys IC Validator provide comprehensive design rule checking tailored for photonic designs, addressing unique challenges arising from curvilinear structures' prevalence.

These verification tools conduct optical and electrical rule checking, focusing on critical aspects such as minimum feature sizes, layer-to-layer spacing, and alignment tolerances, significantly affecting device performance.

Moreover, equation-based design DRC methodologies are often implemented, utilizing multi-dimensional tolerance values to verify curved geometries effectively, thus minimizing photomask errors and ensuring designs are optimized for both manufacturability and performance.2,10

Foundry-Specific Guidelines

Standard Process Design Kits (PDKs)

Process design kits (PDKs) are a vital link between designers and foundries, providing comprehensive libraries of essential photonic components that ensure manufacturability and performance.

Initially limited to basic layouts and fabrication details, PDKs now include parametric cells (PCells) for flexible, foundry-compliant designs, along with detailed layer definitions, design rules, and advanced device models for accurate circuit simulation, allowing designers to predict and optimize performance.

PDKs also facilitate intellectual property protection for foundries by encapsulating key technology characteristics in black box representations, allowing for performance guarantees while safeguarding proprietary manufacturing techniques.

Designers can even create custom components using PDKs, provided they comply with foundry rules regarding material stacks, spacing between optical elements, etching depths, and feature sizes, ensuring compatibility and manufacturability in the design process.2,11

Design for Manufacturability (DFM)

DFM guidelines extend beyond basic design rules to optimize layout and component placement to maximize production yield during integrated circuit development. These guidelines enhance the likelihood of achieving high yields and consistent performance across fabricated chips.

Incorporating DFM guidelines early in the design stage results in cost savings and improved quality but also accelerates time to market and fosters enhanced collaboration between design and manufacturing teams, ensuring that products are innovative and practical to manufacture.10,12

Design for Hybrid Integration

Hybrid integration represents one of the most promising yet challenging frontiers in photonic integrated circuit design, combining different materials and functionalities to create more capable and versatile devices.

This approach enables the integration of components with complementary properties, such as III-V lasers with other passive platforms such as silicon, nitride, lithium niobate photonics and others, but presents significant challenges that must be carefully addressed during the design phase.

Material Compatibility: A primary challenge is material compatibility, where disparities in lattice constants can lead to defects and performance degradation. For instance, the lattice mismatch between silicon and III-V materials like indium phosphide can exceed 8%, risking dislocation. However, techniques such as strain relief, buffer layers, molecular and adhesive bonding as well as flip-chip and edge coupling can be implemented to mitigate these issues and facilitate integration.

Optical Coupling Efficiency: The refractive index contrast between Indium phosphide (InP) and silicon hinders effective optical coupling, resulting in signal losses. Optimized waveguide structures such as tapers can enhance coupling efficiency and improve light transmission between the materials.

Fabrication Process Integration: The distinct fabrication processes for InP and silicon complicate hybrid integration efforts. A multi-step fabrication approach that combines standard silicon processes with regrowth techniques for InP can address these challenges while preserving device performance.

Thermal Management: Differences in thermal conductivity between materials create thermal management challenges that must be addressed. Implementing heat sinks, thermal vias, and effective design strategies ensures adequate heat dissipation, preventing overheating and maintaining device functionality.

Device Reliability: Varying aging mechanisms among materials can negatively impact overall device reliability and performance. Designers employ rigorous testing protocols and advanced encapsulation techniques to ensure long-term stability and protect sensitive interfaces from environmental factors. These strategies enable hybrid devices to achieve operational lifetimes exceeding 25 years, meeting the high demands of telecommunications and data center applications.

Despite the challenges, hybrid integration allows for combining the light generation capability of III-V semiconductors with the CMOS leveraged waveguiding of silicon photonics, enabling devices with unprecedented performance.

As design methodologies and fabrication techniques improve, hybrid integrated photonic circuits are set to advance applications in high-speed communications and quantum computing.13,14

Conclusion

Adherence to industry design guidelines is essential for success in the rapidly evolving PIC field. These standards ensure interoperability, manufacturability, and consistent performance, enabling designers and engineers to navigate common challenges while complying with industry norms. As PICs advance, these guidelines will evolve to address new challenges and opportunities.

The growing PIC industry presents exciting opportunities for skilled professionals knowledgeable in both photonics and electronics. Continuous learning and skill development will empower individuals to contribute to transformative innovations that shape global communication and computing infrastructure. By understanding and applying these design guidelines, engineers and designers can create next-generation PICs that will power the technologies of tomorrow.

The PhotonDelta Challenge

PhotonDelta has launched a Global Photonics Engineering Contest, in collaboration with Wevolver, to drive innovation in applications for PICs across sectors such as healthcare, autonomous vehicles, AI, and agriculture. The contest offers a €50,000 prize in services for the winning concept, global exposure at an industry event, and a chance to receive up to €2 million in pre-seed funding. The event is backed by a €60 million fund from PhotonDelta and industry leaders, including SMART Photonics, LioniX International, Bright Photonics, Epiphany, and PHIX Photonics Assembly. The contest will be officially launched at the PIC Summit 2024 in Eindhoven, Netherlands, on October 15, with submissions open until March 3, 2025, and winners announced on April 2, 2025.

Prize: €50,000 worth of services from the PhotonDelta ecosystem to to make your idea market-ready + a chance to receive up to €2 million in pre-seed funding.

Audience: Open to all engineers, researchers, OEMs, hardware manufacturers, startups/scale-ups, research teams, and students working on innovative PIC applications.

End date: March 3rd 2025

Early Bird Opportunity: All submissions received by 31st December 2024, will receive personalized feedback from PhotonDelta engineers.

References

Yole Intelligence. (2024). Silicon Photonics 2024 - Focus on SOI, SiN, and LNOI platforms. https://www.yolegroup.com/product/report/silicon-photonics-2024/

Khan, M. U., Xing, Y., Ye, Y., & Bogaerts, W. (2019). Photonic integrated circuit design in a foundry+ fabless ecosystem. IEEE Journal of Selected Topics in Quantum Electronics, 25(5), 1-14. https://doi.org/10.1109/JSTQE.2019.2918949

Goodvin. (2024). Reduce Insertion Losses in PLC Chips With Waveguide Structure Optimizations. https://www.opelink.com/blog/reduce-insertion-losses-in-plc-chips-with-waveguide-structure-optimizations_b0170.html

PHIX. (2024). Design Guidelines for Photonic Integrated Circuit Packaging. https://www.phix.com/wp-content/uploads/2021/03/PHIX-Design-Guidelines.pdf

IPSR. (2020). Packaging TWG. https://www.photonicsmanufacturing.org/sites/default/files/documents/_packaging.pdf

Cadence System Analysis. (2024). Thermal Crosstalk in Photonic Integrated Circuits. (2024). https://resources.system-analysis.cadence.com/blog/msa2022-thermal-crosstalk-in-photonic-integrated-circuits

Tech briefs. (2013). Photonics Design Automation - Taking a Building Block Approach to Optical Chip Design. https://www.techbriefs.com/component/content/article/15547-photonics-design-automation

Vafaei, R. et al. (2024). State-of-the-art electronic photonic design automation. https://picmagazine.net/article/118134/State-of-the-art_electronic_photonic_design_automation

Lumerical. (2024). Optical Solvers for Integrated Optical Components. https://www.lumerical.com/learn/whitepapers/optical-solvers-for-integrated-optical-components/

Dhaval S. Shukla. (2024). Understanding the Importance of Prerequisites in the VLSI Physical Design Stage. https://www.design-reuse.com/articles/54634/understanding-the-importance-of-prerequisites-in-the-vlsi-physical-design-stage.html

Synopsys. (2024). What is a Process Design Kit? https://www.synopsys.com/glossary/what-is-a-process-design-kit.html

SemiEng. (2024). Design for Manufacturing (DFM). https://semiengineering.com/knowledge_centers/eda-design/methodologies-and-flows/design-for-manufacturing-dfm/

Karlsruhe Institute of Technology. (2024). Hybrid Photonic Integrated Circuits. https://www.ipq.kit.edu/hybrid_pic.php

Smith, J. A., Jevtics, D., Guilhabert, B., Dawson, M. D., & Strain, M. J. (2022). Hybrid integration of chipscale photonic devices using accurate transfer printing methods. Applied Physics Reviews, 9(4). https://doi.org/10.1063/5.0121567