CPLD vs FPGA: A Comprehensive Technical Analysis and Implementation Guide

This article presents a comprehensive technical analysis of CPLD vs FPGA, focusing on their architectural distinctions, performance metrics, design flows, and implementation methodologies.

Introduction

Programmable Logic Devices (PLDs) represent a fundamental class of integrated circuits that enable hardware functionality reconfiguration post-manufacturing. Complex Programmable Logic Devices (CPLDs) and Field-Programmable Gate Arrays (FPGAs) stand as the two primary architectures in modern programmable logic, each employing distinct approaches to implementing digital circuits. These devices serve as the cornerstone of flexible hardware design, enabling rapid prototyping, field updates, and custom digital solutions across industries from telecommunications to aerospace.

The architectural divergence in CPLD vs FPGA manifests in their internal structure, memory organization, performance characteristics, and implementation methodologies. CPLDs utilize a centralized architecture with AND-OR arrays, while FPGAs employ a distributed array of configurable logic blocks. By exploring CPLD vs FPGA in-depth, this guide aims to provide insights into selecting the appropriate device for specific projects. Whether designing a cost-effective solution or a high-performance system, understanding CPLD vs FPGA is essential for modern electronic design.

Architectural Foundations and Key Differences

The fundamental architectural divergence between CPLDs (Complex Programmable Logic Devices) and FPGAs (Field-Programmable Gate Arrays) is rooted in their core structural organization. This distinction significantly impacts their performance, flexibility, and use cases, making it critical for engineers to understand the principles that govern these devices.

Internal Structure and Organization

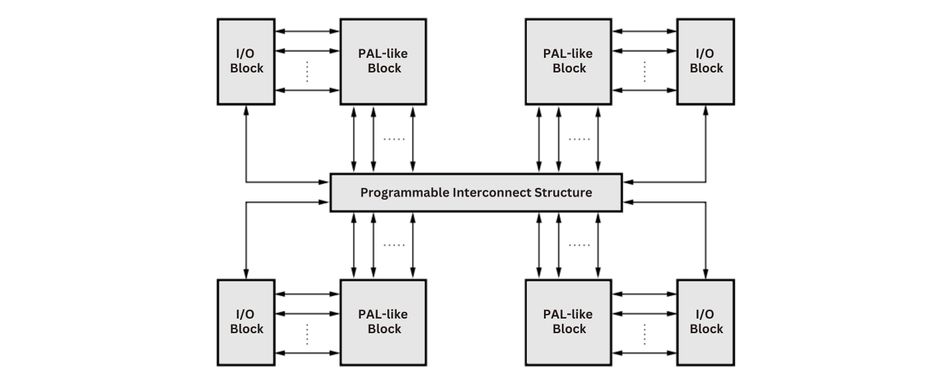

CPLDs employ a centralized architecture centred around AND-OR arrays, forming a monolithic structure designed for direct and efficient signal routing. The architecture includes Programmable Array Logic (PAL) blocks, which combine programmable interconnections with fixed-function logic. [1] These fixed interconnections ensure deterministic timing characteristics, making CPLDs ideal for applications that demand precise and predictable signal propagation. The predictable nature of the interconnections simplifies the design process and enhances reliability in timing-sensitive systems. This centralized structure inherently limits the flexibility of CPLDs but allows for efficient implementation of simple combinatorial logic circuits.

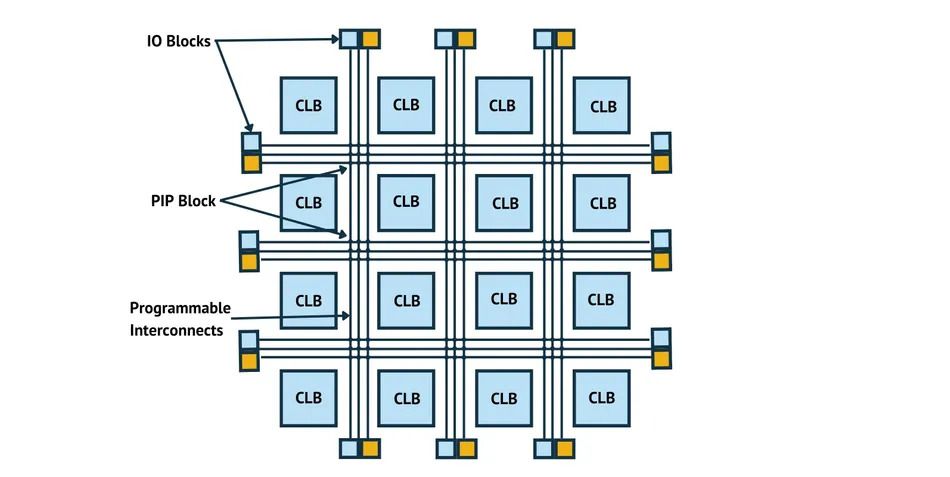

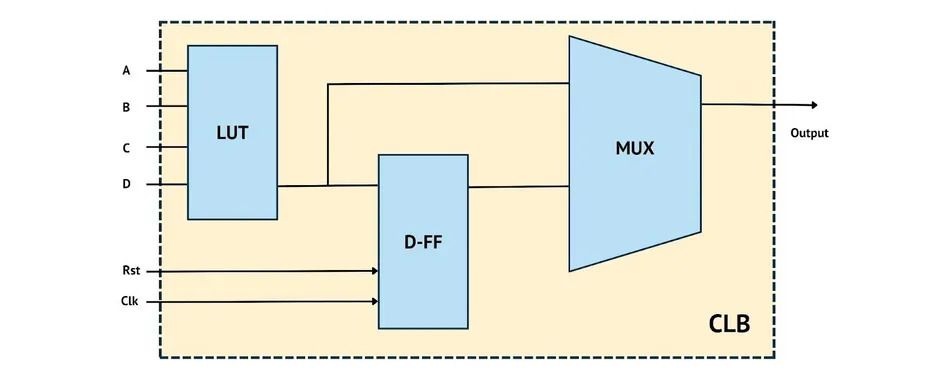

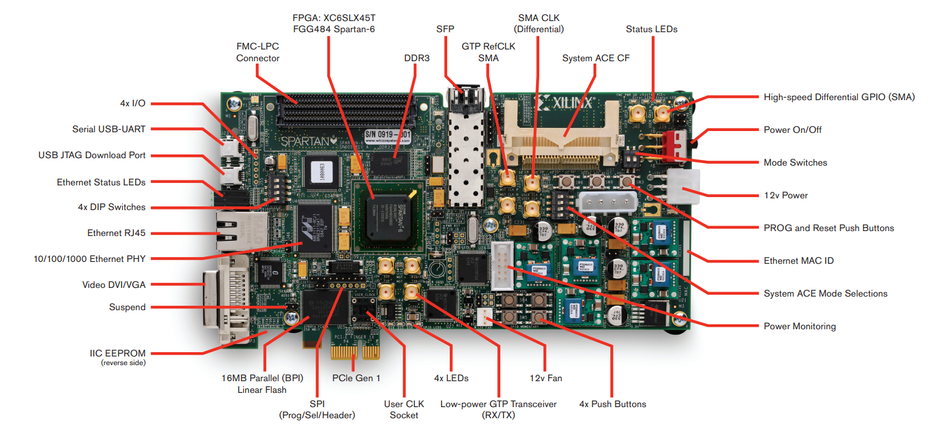

In contrast, FPGAs utilize a distributed architecture based on an array of Configurable Logic Blocks (CLBs) interconnected through a dynamic mesh. Each CLB integrates look-up tables (LUTs), flip-flops, and multipliers, enabling complex logic functions and parallel processing. [2] This modular and distributed approach provides high configurability, allowing engineers to design intricate circuits tailored to specific application requirements. This programmable interconnect fabric supports flexible routing paths, enabling the implementation of high-performance systems with optimized signal propagation.

Let’s go through some of the key architectural differences:

| Feature | CPLD | FPGA |

| Architecture | Centralized | Distributed |

| Logic Blocks | Macrocells with PAL logic | Configurable Logic Blocks (CLBs) |

| Interconnect Structure | Fixed Interconnects | Dynamic Mesh Interconnects |

| Flexibility | Less Flexible | Highly Flexible |

| Typical Use Cases | Simple Logic Implementation, Timing Sensitive Applications | Complex Logic Functions, High-Performance Applications |

The centralized architecture of CPLDs makes them particularly suited for smaller-scale designs, such as glue logic or state machines. Their deterministic timing ensures reliability in applications like industrial controllers and consumer electronics. Conversely, the distributed architecture of FPGAs provides scalability, enabling their use in AI accelerators, networking devices, and aerospace systems. In this, parallelism and high processing throughput are crucial.

Memory Architecture and Distribution

CPLDs are a subset of Simple Programmable Logic Devices (SPLDs) but offer greater complexity and scalability. They use Programmable Logic Array (PLA) structures as their building blocks, with centralized architecture designed for logic cells. CPLDs implement a centralized memory architecture utilizing Flash or EEPROM technology for configuration storage. This monolithic approach features a single, consolidated memory block that maintains device configuration and supports basic logic operations. The memory hierarchy consists of a primary configuration layer and a secondary operational cache, providing deterministic access patterns with typical access speeds of 10 nanoseconds.

The centralized design of CPLD memory limits its scalability and confines it to relatively small memory sizes, usually up to 1MB. While this is sufficient for straightforward digital circuits, it restricts the ability to implement memory-intensive tasks. CPLDs excel in compact designs where simplicity and reliability are prioritized over extensive memory requirements.

FPGAs employ a distributed memory architecture combining SRAM-based configuration memory with embedded Flash blocks. This hierarchical structure incorporates multiple memory tiers: configuration memory, distributed RAM within CLBs, dedicated block RAM modules, and optional external memory interfaces. The distributed approach enables parallel memory access with superior access speeds of 5 nanoseconds, facilitating simultaneous operations across different memory segments.

The memory hierarchy in FPGAs is highly scalable, accommodating internal memory sizes of up to 16MB, with the potential for expansion via external interfaces like DDR4 or HBM. This scalability makes FPGAs suitable for complex applications like machine learning, image processing, and real-time analytics, where significant memory resources are essential.

Below are the key memory characteristics:

| Memory Characteristic | CPLD | FPGA |

| Primary Storage Technology | Flash/EEPROM | SRAM/Flash |

| Memory Capacity | 1MB | 16MB |

| Access Latency | 10ns | 5ns |

| Scaling Potential | Limited | Extensive |

| Architecture Type | Centralized | Distributed |

| Memory Configuration | Fixed | Configurable |

The centralized memory architecture of CPLDs ensures predictable performance and straightforward implementation. This makes them ideal for control systems, ASIC prototyping, and applications with minimal memory demands. On the other hand, the distributed memory architecture of FPGAs supports large-scale designs. This includes video processing pipelines or cryptographic accelerators, where parallel memory access and higher capacity are essential.

Recommended Reading: FPGA Design: A Comprehensive Guide to Mastering Field-Programmable Gate Arrays

Technical Specifications and Performance

Timing Characteristics

The timing characteristics of CPLDs and FPGAs underscore their suitability for distinct applications. The centralized architecture of CPLDs ensures a consistent propagation delay of approximately 5 nanoseconds across their logic paths. [3] This behaviour makes CPLDs ideal for timing-sensitive applications where predictable signal delays are crucial, such as in real-time control systems.

On the other hand, the distributed architecture of FPGAs, with their dynamic routing and advanced interconnects, achieves significantly faster propagation delays of around 3 nanoseconds. This enhanced timing capability allows FPGAs to handle high-performance applications that require complex signal processing and parallel computation, such as AI, ML and high-speed networking.

Another notable difference is in clock speed! CPLDs typically operate at a maximum clock speed of 100 MHz, which aligns well with simpler, less computationally demanding tasks. Conversely, FPGAs achieve clock speeds of up to 300 MHz, supporting data-intensive operations and high-throughput systems. This allows for the implementation of complex CPU architectures, including pipelined and superscalar designs.

Power Characteristics

The power consumption patterns of CPLDs and FPGAs further highlight their distinct operational paradigms. CPLDs, with their Flash/EEPROM-based configuration memory, exhibit lower static power consumption, typically around 50mW. This low-power profile makes CPLDs suitable for battery-operated devices, embedded systems, and portable electronics, where power efficiency is a priority.

FPGAs, employing SRAM-based configuration memory, consume slightly higher static power at approximately 75mW. [4] However, their dynamic power consumption during active operations is significantly greater, reaching up to 250mW, compared to 150mW for CPLDs. This increase is attributed to the distributed routing architecture and the large number of active resources in FPGAs. Despite this, FPGAs excel in high-performance scenarios where power consumption is secondary to computational capacity.

Let’s go through their performance metrics comparison:

| Performance Metric | CPLD | FPGA |

| Clock Speed (MHz) | 100 | 300 |

| Propagation Delay (ns) | 5 | 3 |

| Static Power (mW) | 50 | 75 |

| Dynamic Power (mW) | 150 | 250 |

Both CPLDs and FPGAs leverage advanced power optimization strategies to enhance efficiency and extend device usability in power-sensitive applications:

Utilizing Lower Supply Voltages for Non-Critical Paths: Reducing voltage levels on non-critical paths minimizes power usage while maintaining system performance for essential operations.

Implementing Clock Gating for Unused Circuit Blocks: Clock gating shuts down the clock signal to inactive parts of the circuit, significantly reducing dynamic power consumption.

Employing Dynamic Voltage and Frequency Scaling (DVFS): Adjusting voltage and frequency levels based on workload requirements optimizes power usage dynamically without compromising performance.

Applying Power-Aware Design Methodologies: Designers integrate power constraints during the development phase, ensuring energy-efficient architectures.

Static Power Management Strategies: Techniques such as selective block activation deactivate unused resources, minimizing leakage currents in CPLDs and FPGAs.

The timing and power characteristics of CPLDs and FPGAs reflect their architectural trade-offs and operational focus. CPLDs, with their predictable timing and lower power requirements, are suited for simpler designs and timing-critical applications. FPGAs, with their faster propagation delays and higher performance capabilities, dominate data-intensive domains, although at the cost of increased power consumption. Selecting between CPLDs and FPGAs requires careful evaluation of application-specific demands, balancing performance needs with power efficiency.

Recommended Reading: ASIC vs FPGA: A Comprehensive Comparison

Implementation and Development

Development Environment and Workflow

The development environment for CPLDs and FPGAs includes specialized tools and workflows tailored to their respective architectures. Both platforms rely on integrated development environments (IDEs), which streamline the design, simulation, synthesis, and deployment processes. However, the tools differ in complexity, capabilities, and target applications.

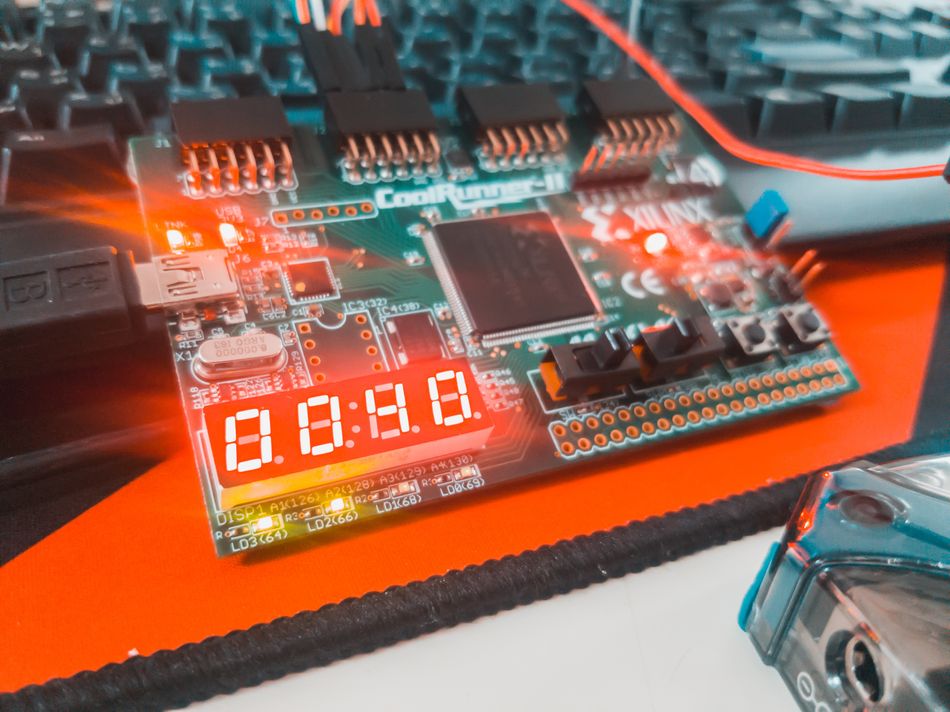

CPLD development typically uses vendor-specific IDEs like Intel Quartus Prime and Xilinx ISE, which are optimized for simpler workflows. These tools emphasize streamlined synthesis and implementation, with user-friendly interfaces designed for straightforward combinatorial and sequential logic design. The synthesis process is fast and predictable, aligning with the timing-sensitive and resource-constrained nature of CPLDs. These tools also support standard Hardware Description Languages (HDLs) such as VHDL and Verilog, focusing on structural design descriptions.

FPGA development requires more comprehensive and feature-rich tools due to the complexity of the designs and the flexibility of FPGA architectures. IDEs such as the Vivado Design Suite (Xilinx), Intel Programmable Solutions Group (Altera) and Intel Quartus Prime Pro provide advanced capabilities like:

High-Level Synthesis (HLS): Enables programming in high-level languages like C/C++ for faster and more intuitive design.

Automated Placement and Optimization: Tools optimize resource utilization, minimize propagation delay and balance power consumption.

Power Estimation and Timing Analysis: Ensures that designs meet stringent performance criteria.

FPGA workflows also support system-level modelling and integration with software-defined hardware tools. This makes them suitable for complex applications such as AI accelerators and network processing units.

Hardware Description Language (HDL) Implementation

HDL usage differs based on the target platform:

CPLD HDL Implementation: CPLDs primarily employ VHDL or Verilog for structural descriptions, focusing on the efficient implementation of combinational logic and state machines. The designs are simpler, with a focus on deterministic timing and low gate counts, making them ideal for small-scale, predictable applications like industrial controllers.

FPGA HDL Implementation: FPGAs support a broader range of HDL capabilities, including RTL-level design and high-level synthesis (HLS) using languages like SystemVerilog, VHDL-2008, and C/C++. This flexibility enables engineers to implement complex, hierarchical designs, including pipelined architectures and parallel processing systems. Advanced tools allow for parameterized designs, IP core integration, and adaptive configurations.

The choice between CPLD and FPGA, as well as the corresponding HDL implementation techniques, depends on the specific requirements of the application.

Configuration Methods

The configuration mechanisms for CPLDs and FPGAs vary significantly, reflecting their architectural and operational differences.

CPLD Configuration:

Interface: Configuration is performed using JTAG-based in-system programming (ISP), a reliable and straightforward method.

Storage: CPLDs rely on non-volatile Flash or EEPROM storage, retaining configuration even after power-down.

Time: Configuration is fast, typically under 1 second, ensuring minimal downtime.

Reconfiguration: Limited support, suitable for applications requiring infrequent updates.

Security: Built-in encryption mechanisms protect configurations from tampering.

FPGA Configuration:

Interface: FPGAs support multiple methods, including JTAG, SPI, and parallel Flash interfaces.

Storage: Configuration is stored in SRAM-based memory, requiring reconfiguration at power-up. Advanced FPGAs integrate on-chip Flash for retaining critical data.

Time: Configuration time ranges from 2 to 10 seconds, depending on the design's complexity.

Reconfiguration: FPGAs excel in dynamic partial reconfiguration, allowing real-time updates to specific regions of the device without disrupting operations.

Security: Advanced features like bitstream encryption, authentication, and tamper detection provide robust protection for critical designs.

Below is the configuration specification comparison:

| Configuration Specification | CPLD | FGPA |

| Programming Interface | JTAG | JTAG, SPI, Parallel |

| Configuration Storage | Flash/EEPROM | SRAM/Flash |

| Configuration Time | <1s | 2-10s |

| Reconfiguration Support | Limited | Dynamic Partial |

| Configuration Security | Built-in Encryption | Advanced Security Features |

By understanding these distinctions, designers can select the appropriate device for their specific application, balancing factors such as configuration speed, flexibility, and security requirements.

Debugging Features and Techniques

Both CPLDs and FPGAs incorporate advanced debugging tools and methodologies to ensure design accuracy and optimize performance:

Integrated Logic Analyzer (ILA) Cores: Real-time signal monitoring enables designers to observe internal signals and diagnose issues directly within the hardware.

JTAG-Based Boundary Scan Testing: Boundary scan tests verify connections and detect faults in the design, facilitating robust hardware debugging.

Hardware Breakpoints and Trigger Conditions: These features allow designers to halt execution at critical points to analyze behaviour and troubleshoot.

Real-Time Power and Performance Monitoring: Tools provide insights into power consumption patterns and operational performance, helping optimize resource usage.

Automated Timing Analysis and Constraint Verification: Automated tools check for timing violations and ensure that the design meets specified constraints.

Signal Force/Release Functionality: Enables precise control over internal signals during debugging, allowing designers to simulate various scenarios.

The implementation and development workflows for CPLDs and FPGAs cater to their distinct architectures and use cases. CPLDs offer a streamlined development process, ideal for simpler designs with predictable requirements. In contrast, FPGAs provide a comprehensive ecosystem for designing and optimizing complex systems. [5] The choice between CPLDs and FPGAs depends on the complexity, resource requirements, and the need for flexibility in applications. This makes it easy to understand their workflows and tools critical for successful implementation.

Recommended Reading: Verilog vs VHDL: A Comprehensive Comparison

Use Cases and Applications

CPLD Applications

CPLDs excel in applications that demand deterministic timing, low complexity, and efficient resource utilization. Their centralized architecture and predictable performance make them useful in several domains:

Industrial Controllers:

CPLDs, with their simpler architecture, are widely used in timing-critical control systems, where low-latency operations and precise timing are crucial.

For example, they are deployed in factory automation, robotics control, and process instrumentation, ensuring reliability in tasks such as motor control and signal synchronization.

The non-volatile memory of CPLDs ensures the device retains its logic even during power outages, aligning with applications like microcontroller interfacing in industry.

Consumer Electronics:

CPLDs are ideal for low-complexity designs where consistent performance and cost efficiency are priorities.

Applications include home appliances, digital clocks, display drivers, and input/output controllers.

Their simplicity allows for rapid prototyping and deployment in consumer-grade devices that do not require extensive configurability or logic capacity.

Glue Logic:

CPLDs serve as interface devices to connect different digital components within a system, especially when components operate on incompatible protocols.

For instance, in legacy system integration, CPLDs bridge communication between older components and newer microprocessors, ensuring smooth data flow.

They are also used for address decoding, chip-select generation, and protocol conversion, providing quick and efficient solutions for specific interfacing challenges.

CPLD architecture is suited well for applications including protocol conversion, address decoding, and single-chip interfacing in integrated circuits. Similarly, they are ideal for low-complexity designs like I/O pins, display drivers, and microprocessor interfacing.

FGPA Applications

FPGAs are designed to handle high-performance, complex logic, and parallel processing tasks, making them ideal for a broad range of advanced applications:

High-Performance Computing:

FPGAs play a key role in artificial intelligence (AI) and machine learning systems, particularly in semiconductor-based AI accelerators and neural network processing units (NPUs). Their ability to implement customizable parallelism ensures efficient execution of compute-intensive algorithms.

In data analytics, FPGAs are used to accelerate tasks such as pattern recognition, image processing, and real-time data analysis, enabling faster insights with lower latency compared to traditional processors.

Cloud platforms like AWS and Microsoft Azure offer FPGA-based services to boost computational efficiency for enterprise-level applications.

Telecommunications:

FPGAs are widely deployed in digital signal processing (DSP) tasks, such as baseband processing in 5G networks, modulation/demodulation, and error correction coding.

Their configurability allows telecommunication systems to adapt to evolving standards, such as LTE to 5G upgrades, without requiring hardware replacement.

Protocol emulation is another key area where FPGAs shine, enabling the testing and development of communication protocols like Ethernet, CAN, and PCIe in networking devices.

Aerospace and Defense:

The real-time data acquisition capabilities of FPGAs make them essential for radar systems, sonar processing, and unmanned aerial vehicle (UAV) control.

The ability of FPGA to perform high-throughput parallel processing ensures reliable performance in mission-critical applications, such as missile guidance systems, space exploration, and satellite communication.

Their dynamic reconfiguration capabilities allow for in-field updates to adapt to changing mission requirements, ensuring longevity and versatility in high-stakes environments.

Understanding these distinct applications allows designers to make informed decisions, leveraging CPLDs for cost-efficient, timing-critical designs and FPGAs for complex, high-performance solutions. By leveraging the right type of programmable logic device, engineers can optimize their PCB designs to achieve efficiency, performance, and reliability.

Recommended Reading: What is an ASIC: A Comprehensive Guide to Understanding Application-Specific Integrated Circuits

Conclusion

The architectural distinctions between CPLDs and FPGAs manifest in their performance characteristics. CPLDs offer deterministic timing and simplified routing at the cost of flexibility while FPGAs provide superior scalability and resource utilization through their distributed architecture. Device selection should prioritize specific application requirements, including timing constraints, power budget, and complexity of logic implementation.

Implementation success depends on matching device characteristics with project requirements. CPLDs excel in applications requiring fast response times, simple combinatorial logic, and deterministic behavior. FPGAs prove optimal for complex digital systems, parallel processing requirements, and applications demanding significant memory resources or dynamic reconfiguration capabilities.

Frequently Asked Questions

Q: How can I optimize CPLD performance for timing-critical applications?

A: Implement synchronous design practices, minimize combinatorial logic depth, and utilize dedicated clock networks. Consider partitioning complex logic across multiple PAL blocks to reduce propagation delays.

Q: What debugging approaches are most effective for FPGA designs?

A: Utilize integrated logic analyzers for real-time signal monitoring, implement JTAG-based debugging cores, and employ systematic signal probing. Implement comprehensive test benches and use hardware-in-the-loop testing for complex scenarios.

Q: How should I approach migrating designs between CPLDs and FPGAs?

A: Begin with a thorough analysis of timing requirements and resource utilization. Restructure combinational logic for the target architecture, adjust clock domain crossing mechanisms, and validate timing constraints on the new platform.

Q: What are the key considerations for power optimization in FPGA designs?

A: Implement clock gating for unused blocks, utilize power-aware placement and routing, and employ voltage scaling where applicable. Consider using dedicated hardware blocks instead of soft logic for frequently used functions.

Q: How can I ensure reliable configuration in SRAM-based FPGAs?

A: Implement configuration error detection and correction, use dedicated configuration monitoring circuits, and employ redundant configuration storage. Consider implementing configuration verification routines during startup.

References

[1] ScienceDirect. Chapter 2 - Field-Programmable Logic in Book: Top-Down Digital VLSI Design [Cited 2024 November 15] Available at: Link

[2] FPGAinsights. LUT in FPGA: Lookup Tables (LUT) in FPGA Design (2024) [Cited 2024 November 15] Available at: Link

[3] icdrex. Understanding CPLD (Complex Programmable Logic Device) [Cited 2024 November 15] Available at: Link

[4] intechopen. Power Efficient Data-Aware SRAM Cell for SRAM-Based FPGA Architecture [Cited 2024 November 15] Available at: Link

[5] MicrochipUSA. CPLDs vs. FPGAs: Understanding the Differences and Choosing the Right Solution [Cited 2024 November 15] Available at: Link

Table of Contents

IntroductionArchitectural Foundations and Key DifferencesInternal Structure and OrganizationMemory Architecture and DistributionTechnical Specifications and PerformanceTiming CharacteristicsPower CharacteristicsImplementation and DevelopmentDevelopment Environment and WorkflowHardware Description Language (HDL) ImplementationConfiguration Methods Debugging Features and Techniques Use Cases and ApplicationsCPLD ApplicationsFGPA ApplicationsConclusionFrequently Asked QuestionsReferences