ASIC Design: From Concept to Production

ASICs, or Application-Specific Integrated Circuits, are specialized chips designed to perform specific tasks with high efficiency and precision, offering a powerful solution for a wide range of industries and applications.

Introduction

Application-Specific Integrated Circuit (ASIC) design has become an increasingly important aspect of the technology industry as companies and design teams strive to create specialized solutions for a variety of applications. In this comprehensive guide, we will explore ASIC design, providing an in-depth look at the entire process from concept to production. This article is intended for readers who are interested in learning about ASIC design flow, whether they are industry professionals, students, or simply curious about the technology.

Throughout this guide, we will cover various topics related to ASIC system design, including the key differences between ASICs and other integrated circuits, the stages of the ASIC design process, manufacturing considerations, and testing and validation procedures. We will also discuss the tools and resources available to ASIC designers and current trends and future developments in the field. By the end of this article, you will have a solid understanding of the principles and practices involved in ASIC design, setting the foundation for further exploration and learning.

What is ASIC Design?

Application-Specific Integrated Circuit (ASIC) design refers to the process of creating custom integrated circuits tailored to perform specific functions for a particular application. Unlike general-purpose integrated circuits, such as Field-Programmable Gate Arrays (FPGAs) and microcontrollers, ASICs are designed with a single purpose in mind, which enables them to deliver superior performance, power efficiency, and cost-effectiveness for their intended tasks.

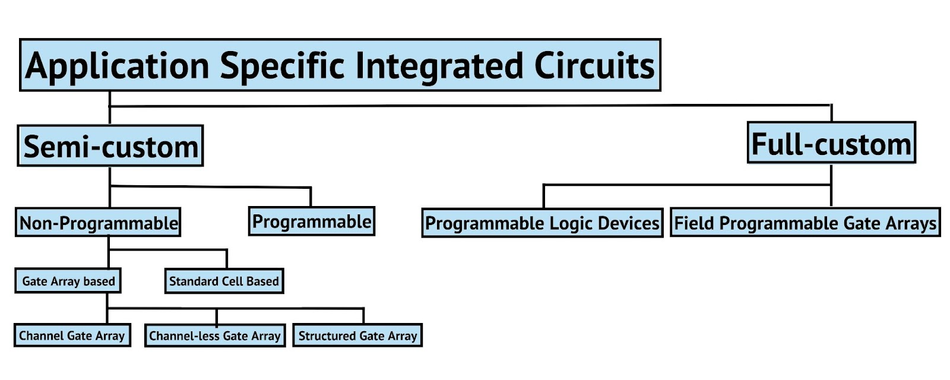

Types and Classification of ASICs

There are different types of ASICs, each with varying levels of customization and design complexity.

Full-custom circuits

Full-custom ASICs allow for the highest level of customization and optimization. Designers have complete control over every aspect of the chip, including transistor sizing, layout, and interconnects. This level of customization results in optimal performance, power efficiency, and area usage. However, full-custom ASICs require a significant amount of design effort and have a longer time-to-market.

Programmable Logic Devices (PLDs) are a category of integrated circuits that feature configurable logic components and interconnects. Users can program these devices to create custom logic functions tailored to specific needs. FPGAs are a more advanced type of PLD that offer additional features, including embedded memory blocks, digital signal processing blocks, and high-speed I/O capabilities, enabling more complex and high-performance applications.

Semi-custom ASICs

Semi-custom ASICs, also known as standard-cell ASICs, use pre-designed building blocks called standard cells to create the desired functionality. These standard cells include commonly used logic gates, memory elements, and other functional components. Semi-custom ASICs offer a balance between customization and design complexity, making them a popular choice for many applications. They require less design effort compared to full-custom ASICs but may not achieve the same level of optimization.

Non-programmable Semi-custom ASICs comprise two main classifications: gate array-based and standard cell-based designs.

Gate Array-based ASICs design approach involves prefabricated silicon wafers containing arrays of uncommitted transistors. Designers can create the desired functionality by adding custom metal interconnect layers to connect the transistors. Gate Array-based ASICs can be further divided into three types:

Channel Gate Array: This design involves a prefabricated silicon wafer with an array of uncommitted transistors. A custom metal interconnect layer is used to connect the transistors, forming the desired functionality. This approach offers a balance between customization and development time.

Structured Gate Array (Embedded Array): Similar to channel gate arrays, structured gate arrays feature a higher level of integration. They contain a mix of prefabricated components and customizable elements, providing better performance and customization potential compared to traditional channel gate arrays.

Channel-less Gate Array: This evolution of the channel gate array eliminates predefined channels between logic blocks, resulting in improved area utilization and performance. This design allows for greater flexibility in the placement and interconnection of components.

Standard Cell-based ASICs (Non-programmable Semi-custom ASICs), on the other hand utilize pre-designed building blocks, known as standard cells, to create the desired functionality. Standard cells include commonly used logic gates, memory elements, and other functional components. This approach offers a balance between customization and design complexity, making it a popular choice for a wide range of applications. By leveraging standard cells, designers can reduce development time and effort while still achieving a high level of customization.

Advantages of ASICs

Understanding the advantages and disadvantages of ASICs is crucial for determining whether they are the right choice for a given project. There are several advantages to using ASICs in various applications, including:

Performance: ASICs are optimized for their specific tasks, which means they can deliver higher performance compared to general-purpose integrated circuits.

Integration: ASICs enable the integration of multiple functions and components onto a single chip, reducing the overall complexity and size of the system. This is particularly beneficial for compact devices and systems with strict size constraints.

Customization: ASICs offer a high level of customization, allowing designers to create chips tailored to the exact requirements of their application. This results in improved efficiency and better alignment with the system's needs.

Reliability: Due to their specialized design and the integration of components on a single chip, ASICs can offer improved reliability compared to systems built using multiple off-the-shelf components. This is particularly important for mission-critical applications.

Intellectual Property (IP) Protection: ASICs can better protect proprietary technologies and intellectual property, as they are harder to reverse-engineer than software-based or FPGA-based solutions.

Reduced Electromagnetic Interference (EMI): By integrating multiple components on a single chip and optimizing the layout, ASICs can reduce EMI, which improves overall system performance and complies with regulatory standards.

Power Efficiency: ASICs consume less power than their general-purpose counterparts due to their specialized nature, making them ideal for energy-sensitive applications.

Cost-Effectiveness at scale: Although the initial development costs for ASICs can be high, the per-unit cost decreases significantly with large production volumes, making them more cost-effective in the long run.

Disadvantages of ASICs

Despite their benefits, ASICs also have some drawbacks:

Development Costs: The initial investment required for ASIC chip design and manufacturing can be quite high, especially for small production runs.

Time to Market: The ASIC circuit design process can be lengthy, which may result in a long time to market compared to using off-the-shelf components.

Flexibility: Unlike FPGAs and microcontrollers, ASICs are designed for specific applications and cannot be reprogrammed or reconfigured for other purposes.

In the following sections, we will delve deeper into the ASIC design process to provide a better understanding of the various stages involved and the key factors to consider throughout the process.

The ASIC Design Process

The ASIC logic design process is a complex and iterative journey involving several stages, each with its own set of challenges and considerations. A thorough understanding of these stages is essential for successfully bringing an ASIC design specification from concept to production. The main stages of the ASIC development process include the following:

Specification and Requirements

Architecture and High-Level Design

RTL Design and Design Verification

Logic Synthesis and Optimization

Physical Design and Layout

Signoff and Tapeout

1. Specification and Requirements

The first stage in the ASIC design cycle involves defining the specifications and requirements for the project. This includes outlining the desired functionality, performance goals, power consumption targets, and other critical parameters. It is essential to gather input from all relevant stakeholders, such as system architects, hardware designers, software developers, ASIC design engineers, and product managers, to ensure that the final ASIC meets the needs of the intended application.

2. Architecture and High-Level Design

Once the specifications and requirements are established, the next step is to create the ASIC architecture and high-level design. This involves selecting the appropriate components, such as processors, memory blocks, and communication interfaces, as well as defining the interconnects between them. During this stage, designers must carefully consider trade-offs between performance, power consumption, and area to achieve the optimal balance for the target application.

3. RTL Design and Design Verification

The Register-Transfer Level (RTL) design stage involves translating the high-level architecture into a hardware description language (HDL), such as Verilog, System Verilog, or VHDL. This representation describes the behavior of the ASIC in terms of registers, combinational logic, and clock domains. RTL design is followed by verification, which entails simulating and testing the design on the test bench to ensure that it meets the specified requirements and functionality. Design verification is a critical step in the design process, as it helps identify, address, and debug potential issues before moving on to the next stages.

4. Logic Synthesis and Optimization

During the synthesis stage, the RTL design is converted into a gate-level netlist, which represents the ASIC in terms of transistors, logic gates, and interconnects. This process involves mapping the RTL code to a specific technology library or algorithm provided by the chosen semiconductor foundry. Once the gate-level netlist is generated, designers perform optimization to meet the desired performance, power, and area targets. This may involve adjusting the design, modifying the technology library, or fine-tuning synthesis settings.

5. Physical Design and Layout

The physical design stage involves converting the gate-level netlist into a physical layout that can be manufactured by the semiconductor foundry. This process includes floorplanning, placement, and routing of the various components and interconnects within the ASIC. During this stage, designers must place and route components while considering factors such as signal integrity, power distribution, and thermal management to ensure a robust and reliable final product.

6. Signoff and Tapeout

The final stage in the ASIC design process is signoff and tape out. This involves verifying the physical layout against design rules provided by the foundry, as well as performing layout-versus-schematic (LVS) checks to ensure that the layout accurately represents the intended design. Once the design has passed these checks, it is "taped out" and sent to the foundry for manufacturing.

FPGA (Field-Programmable Gate Array) design techniques, which involve the configuration of programmable logic devices, can serve as a precursor to ASIC development, allowing designers to prototype and validate their designs before committing to the more expensive and time-consuming ASIC production process.

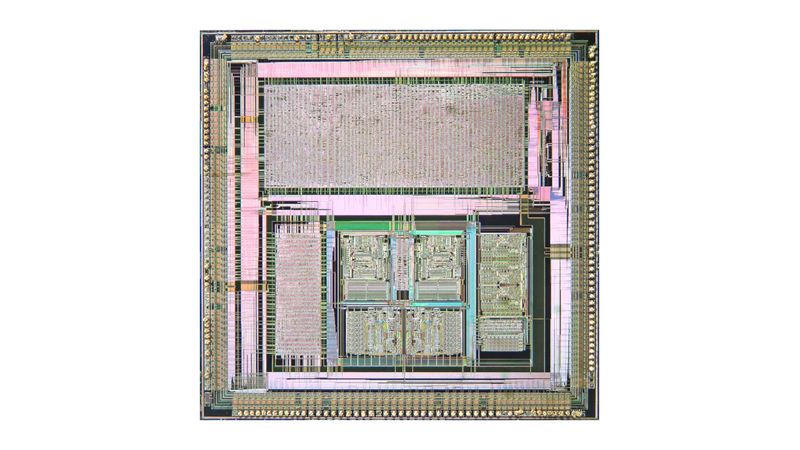

ASIC Manufacturing

Once the ASIC design has been finalized and taped out, the next step is manufacturing the integrated circuit. This process involves several stages, including wafer fabrication, die preparation, packaging, and assembly. Selecting the right fabrication technology and foundry partner is crucial for achieving the ASIC's desired performance, power efficiency, and cost targets.

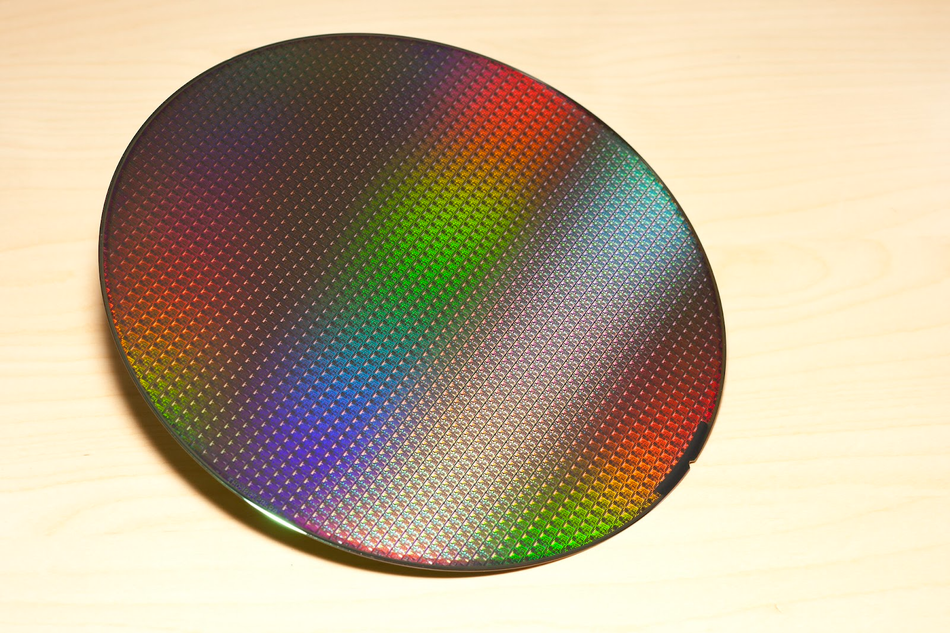

Wafer Fabrication

Wafer fabrication is the process of creating the ASIC on a silicon wafer using a series of photolithography, etching, and deposition steps. The choice of fabrication technology, often referred to as the process node (e.g., 7nm, 14nm, 28nm), has a significant impact on the performance, power consumption, and area of the final ASIC. Smaller process nodes generally offer higher performance and low power consumption but come with increased manufacturing complexity and cost.

Die Preparation

After the wafer fabrication is complete, the individual ASIC dies are separated from the wafer through a process called dicing. Each die is then inspected and tested to ensure that it meets the specified requirements and performance targets. Defective dies are discarded, while functional dies move on to the packaging and assembly stage.

Packaging and Assembly

The packaging stage involves encapsulating the ASIC die in a protective custom-design casing that provides mechanical support, thermal management, and electrical connections to the outside world. There are several packaging technologies available for ASICs, each with its own set of advantages and trade-offs. Some of the most common packaging technologies include:

Wire-bond: This technology involves connecting the ASIC die to the package substrate using thin wires. Wire-bond packaging is relatively low-cost and widely used but may have limitations in terms of electrical performance and scalability.

Flip-chip: In flip-chip packaging, the ASIC die is flipped upside-down and connected to the package substrate using solder bumps. This technology offers better electrical performance and a smaller form factor than wire-bond but may have higher costs and complexity.

Through-Silicon Vias (TSVs): TSV packaging involves creating vertical electrical connections through the silicon die itself, enabling the creation of 3D stacked integrated circuits. This technology offers significant benefits in terms of performance, power efficiency, and form factor but can be more complex and expensive than other packaging options.

The choice of packaging technology depends on factors such as performance requirements, form factor constraints, and cost considerations.

During assembly, the packaged ASICs are mounted onto printed circuit boards (PCBs) and connected to other components, such as passive devices, connectors, and heat sinks.

Selecting the right packaging and assembly partner is essential for achieving the desired performance, reliability, and cost targets for the ASIC. Key factors to consider when choosing a partner include their experience, technical capabilities, capacity, and track record in the industry.

In the next sections, we will discuss the testing and validation procedures that follow the manufacturing process, as well as the tools and resources available to ASIC designers.

Testing and Validation

After the ASIC has been manufactured, it is essential to perform thorough testing and validation to ensure that the final product meets the specified requirements, functionality, and performance targets. This process involves a combination of functional testing, performance testing, and reliability testing to identify and address any potential issues before the ASIC is deployed in the target application.

Functional Testing

Functional testing is the process of verifying that the ASIC performs its intended functions correctly. This involves applying a set of input stimuli to the ASIC and comparing the resulting output against the expected behavior defined in the specifications. Functional testing can be performed at various levels, including the die, package, and system level, depending on the complexity of the ASIC and the target application.

Performance Testing

Performance testing evaluates the ASIC's performance characteristics, such as processing speed, power consumption, and thermal performance, under various operating conditions. This type of testing is critical for ensuring that the ASIC meets the performance targets outlined in the specifications and can operate reliably in the intended application environment. Performance testing may involve a combination of simulation, bench testing, and in-system testing, depending on the specific requirements of the project.

Reliability Testing

Reliability testing is conducted to assess the long-term stability and robustness of the ASIC under various stress conditions, such as temperature, voltage, and mechanical stress. This type of testing helps identify potential failure mechanisms and assess the expected lifetime of the ASIC. Reliability testing often involves accelerated life testing, where the ASIC is subjected to extreme conditions to simulate extended periods of operation in a shorter timeframe.

By conducting thorough testing and validation procedures, designers can ensure that the final ASIC product meets the specified requirements and delivers the desired performance, power efficiency, and reliability in the target application.

In the following sections, we will explore the tools and resources available to ASIC designers, as well as current trends and future developments in the field.

ASIC Design Tools and Resources

To successfully design and develop an ASIC, design teams need access to various tools and resources to help them navigate the complex process from concept to production. These tools and resources play a crucial role in each stage of the ASIC design process, enabling designers to create, verify, optimize, and validate their designs effectively. Some popular ASIC design tools and resources include:

Electronic Design Automation (EDA) Tools: EDA tools are software applications that automate various aspects of the ASIC design process, such as schematic capture, simulation, layout, and verification. Popular EDA tool vendors include Cadence, Synopsys, and Mentor Graphics.

Hardware Description Languages (HDLs): HDLs, such as Verilog and VHDL, are programming languages used to describe the behavior and structure of digital circuits, enabling designers to create and verify RTL designs.

Intellectual Property (IP) Cores: IP cores are pre-designed and pre-verified functional blocks that can be integrated into an ASIC design to save time and reduce development costs. Common IP cores include processors, memory blocks, and communication interfaces.

Design Libraries: Design libraries contain collections of standard cells, memory blocks, and other components that are optimized for a specific fabrication technology. These libraries are provided by the semiconductor foundry and are essential for the synthesis and physical design stages.

Verification and Validation Tools: These tools help designers ensure that their designs meet the specified requirements and functionality. Examples include simulation tools, formal verification tools, and hardware emulation platforms.

When selecting ASIC design tools and resources, it is important to consider factors such as compatibility with the chosen fabrication technology, ease of use, scalability, and support from the vendor. Additionally, designers should evaluate the tools' ability to handle the specific requirements and challenges of their projects, such as performance, power consumption, and area constraints.

In the next sections, we will discuss the current trends and emerging technologies in the field of ASIC design, as well as the challenges and opportunities that these developments present for designers.

The Future of ASIC Design

As technology continues to evolve, ASIC design is also experiencing significant changes and advancements. Current trends and emerging technologies are shaping the future of ASIC design, presenting both challenges and opportunities for designers. Some of these developments include:

Advanced Process Nodes

The ongoing push for smaller process nodes, such as 5nm, 3nm, and beyond, is driving improvements in performance and power efficiency for ASICs. However, these advanced nodes also bring increased manufacturing complexity and cost, as well as new design challenges related to signal integrity, power distribution, and reliability.

Heterogeneous Integration

Heterogeneous integration involves combining different types of components, such as processors, memory, and sensors, into a single system-on-chip (soc) to achieve better performance and functionality. This trend is driving the development of advanced packaging technologies, such as 2.5D and 3D integration, which enable the creation of high-performance, compact ASICs with diverse capabilities.

Artificial Intelligence and Machine Learning

The rise of artificial intelligence (AI) and machine learning (ML) applications is driving demand for specialized ASICs, such as AI accelerators and neural network processors, that can deliver high performance and power efficiency for these compute-intensive tasks. This trend is also driving the development of new design methodologies and tools that can help designers create and optimize ASICs for AI and ML applications.

Open-Source Hardware and Tools

The growing interest in open-source hardware and tools, such as the Reduced Instruction Set Computing V (RISC-V) instruction set architecture and open-source EDA tools, is providing designers with more options and flexibility in their ASIC design projects. This trend has the potential to lower barriers to entry, reduce costs, and foster innovation in the ASIC design community.

Security and Trust

As the importance of security and trust in electronic systems grows, ASIC designers are increasingly focusing on incorporating hardware-based security features, such as secure boot, encryption, and authentication, into their designs. This trend is driving the development of new design methodologies, tools, and IP cores that can help designers create secure and trusted ASICs.

By staying informed about these trends and emerging technologies, ASIC designers can better position themselves to address the challenges and seize the opportunities presented by the rapidly evolving landscape of ASIC design.

Frequently Asked Questions (FAQs)

What is the difference between ASICs and FPGAs?

ASICs are custom-designed integrated circuits tailored for specific applications, while FPGAs are reprogrammable integrated circuits that can be configured to perform various functions. ASICs generally offer higher performance and lower power consumption than FPGAs but have higher development costs and longer time-to-market.

How long does it take to design and manufacture an ASIC?

The ASIC design process can take anywhere from several months to a few years, depending on the complexity of the design and the resources available. Manufacturing lead times can also vary, typically ranging from a few weeks to several months, depending on the foundry's capacity and the specific fabrication technology.

What are the key factors to consider when selecting a semiconductor foundry for ASIC manufacturing?

Important factors to consider when choosing a foundry include their experience, technical capabilities, capacity, and track record in the industry. Additionally, designers should evaluate the foundry's support for the chosen fabrication technology and their ability to meet the performance, power, and cost targets for the ASIC.

What are some common challenges in the ASIC design process?

Common challenges in the ASIC design process include meeting performance, power, and area targets; managing design complexity; ensuring signal integrity and power distribution; and addressing reliability and manufacturability concerns.

How can I learn more about ASIC design?

To further your understanding of ASIC design, consider taking courses, attending workshops or conferences, reading books and articles, and participating in online forums and communities related to the field. Additionally, working on hands-on projects and collaborating with experienced professionals can provide valuable insights and practical experience.

Conclusion

In this comprehensive guide, we have explored the world of ASIC design, covering topics such as the differences between ASICs and other integrated circuits, the stages of the ASIC design process, manufacturing considerations, and testing and validation procedures. We also discussed the tools and resources available to ASIC designers, as well as current trends and future developments in the field.

Understanding the principles and practices involved in ASIC design is crucial for anyone interested in this domain. As technology continues to evolve, the importance of ASICs in various applications is only expected to grow. By gaining a solid foundation in ASIC design, you will be better equipped to navigate the challenges and opportunities presented by this rapidly changing landscape.

Table of Contents

IntroductionSemi-custom ASICs1. Specification and Requirements2. Architecture and High-Level Design3. RTL Design and Design Verification4. Logic Synthesis and Optimization5. Physical Design and Layout6. Signoff and TapeoutWafer FabricationPackaging and AssemblyFunctional TestingPerformance TestingReliability TestingAdvanced Process NodesHeterogeneous IntegrationArtificial Intelligence and Machine LearningOpen-Source Hardware and ToolsSecurity and Trust